Sistem Digital:SR-Latch (Gerbang NAND): Difference between revisions

| Line 15: | Line 15: | ||

==Komponen R-S Latch== | ==Komponen R-S Latch== | ||

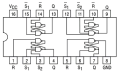

IC 74LS279 berisikan rangkaian R-S Latch. | |||

<gallery> | <gallery> | ||

File:Sr-latch2.png|IC | File:Sr-latch2.png|IC | ||

File:Sr-latch3.png|Kompone R-S Latch | File:Sr-latch3.png|Kompone R-S Latch | ||

</gallery> | </gallery> | ||

==Mengkondisikan 1 “Set” pada NAND Latch== | |||

Setelah dikondisikan Q=1 karena pulsa rendah di S (lihat tabel fungsi gerbang NAND) | |||

[[File:Sr-latch4.png|thumb|center]] | |||

Revision as of 21:44, 26 February 2022

Rangkaian Penahan (Latch)

Rangkaian gerbang digital yang digunakan untuk menahan informasi disebut Latch.

Latch merupakan peranti yang dwimantap, yaitu rangkaian yang memiliki dua keadaan yaitu keadaan 0 atau 1.

Rangkaian latch dapat menyimpan 1 bit biner dari informasi karena menanggapi masukkannya, jika suatu masukkan menyebabkannya berpindah ke keadaan 1. Peranti itu akan tetap menahannya sebagai 1 sampai ada masukkan lain yang menyebabkannya berubah ke keadaan 0.

Demikian juga sebaliknya jika suatu masukkan menyebabkannya berpindah ke keadaan 0. Peranti itu akan tetap menahannya sebagai 0 sampai ada masukkan lain yang menyebabkannya berubah ke keadaan 1.

Rangkaian R-S Latch

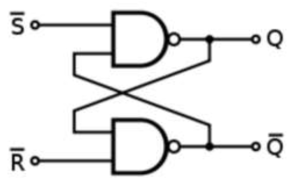

Latch mempunyai dua signal keluaran, yang satu merupakan komplemen dari yang lainnya. Terdapat dua masukkan yaitu S (set) dan R (reset) dan dua buah keluaran yang diberi symbol Q dan Q.

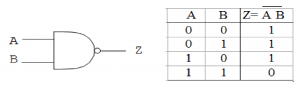

Suatu untai latch dapat dibuat dengan menggunakan beberapa gerbang dasar. S-R latch yang dirangkai dengan menggunakan dua gerbang NAND

Komponen R-S Latch

IC 74LS279 berisikan rangkaian R-S Latch.

-

IC

-

Kompone R-S Latch

Mengkondisikan 1 “Set” pada NAND Latch

Setelah dikondisikan Q=1 karena pulsa rendah di S (lihat tabel fungsi gerbang NAND)