Sistem Digital:Shift Register: Difference between revisions

m Kangtain moved page Materi/Sistem Digital/Shift Register to Sistem Digital:Shift Register |

|||

| (6 intermediate revisions by the same user not shown) | |||

| Line 8: | Line 8: | ||

REGISTER dengan “n-bit” memory terdiri dari sejumlah “n” FLIP FLOP dan mampu menyimpan sebanyak “n-bit” karakter | REGISTER dengan “n-bit” memory terdiri dari sejumlah “n” FLIP FLOP dan mampu menyimpan sebanyak “n-bit” karakter | ||

== | ==Shift Register== | ||

#Suatu register dapat melakukan pergeseran informasi biner ke kiri atau ke kanan disebut register geser. Konfigurasi logika dari sebuah register geser terdiri dari rangkaian flip-flop yang dihubungkan secara cascade, yaitu output dari salah satu flip-flop dihubungkan ke input flip-flop berikutnya. | #Suatu register dapat melakukan pergeseran informasi biner ke kiri atau ke kanan disebut register geser. Konfigurasi logika dari sebuah register geser terdiri dari rangkaian flip-flop yang dihubungkan secara cascade, yaitu output dari salah satu flip-flop dihubungkan ke input flip-flop berikutnya. | ||

#Semua flip-flop menerima pulsa clock dalam waktu yang bersamaan dan menyebabkan pergeseran dari satu keadaan ke keadaan berikutnya. | #Semua flip-flop menerima pulsa clock dalam waktu yang bersamaan dan menyebabkan pergeseran dari satu keadaan ke keadaan berikutnya. | ||

| Line 15: | Line 15: | ||

input data (0 dan 1) digeser dari Data Input ke Data Output. Diperlukan 1 pulsa clock untuk mentransfer tiap bit, yang berarti dibutuhkan 8-pulsa clock untuk transfer 1 byte. | input data (0 dan 1) digeser dari Data Input ke Data Output. Diperlukan 1 pulsa clock untuk mentransfer tiap bit, yang berarti dibutuhkan 8-pulsa clock untuk transfer 1 byte. | ||

[[File:Shift-register 3.png|thumb|center]] | |||

Data Serial dimasukkan ke shift register saat Clock naik. Lachched, Data Serial dipertahankan hingga Clock turun. Data Serial merupakan informasi yang ditampilkan. | |||

[[File:Shift-register 4.png|thumb|center|Rangkaian Shift Register]] | |||

Latest revision as of 23:19, 19 November 2022

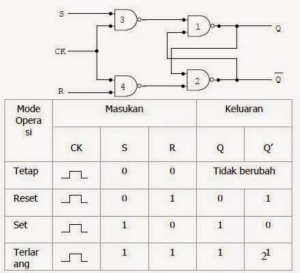

FLIP FLOP adalah sebuah rangkaian sekuensial yang mampu menyimpan 1 bit memory. Untuk membuat sebuah rangkaian sekuensial yang mampu menyimpan 2 atau lebih bit memory didalamnya atau meningkatkan kapasitas memory, dibutuhkan gabungan 2 atau lebih rangkaian FLIP FLOP yang didalamnya.

Register (Penyimpan Data) REGISTER adalah kumpulan FLIP FLOP yang digabungkan menjadi sebuah rangkaian sekuensial yang bertujuan untuk menyimpan n-bit memory

REGISTER dengan “n-bit” memory terdiri dari sejumlah “n” FLIP FLOP dan mampu menyimpan sebanyak “n-bit” karakter

Shift Register

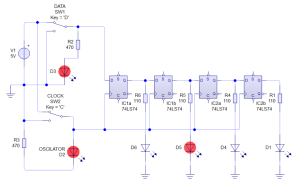

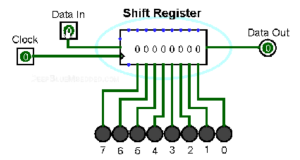

- Suatu register dapat melakukan pergeseran informasi biner ke kiri atau ke kanan disebut register geser. Konfigurasi logika dari sebuah register geser terdiri dari rangkaian flip-flop yang dihubungkan secara cascade, yaitu output dari salah satu flip-flop dihubungkan ke input flip-flop berikutnya.

- Semua flip-flop menerima pulsa clock dalam waktu yang bersamaan dan menyebabkan pergeseran dari satu keadaan ke keadaan berikutnya.

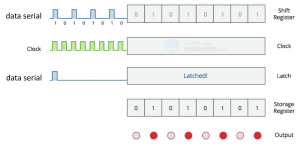

input data (0 dan 1) digeser dari Data Input ke Data Output. Diperlukan 1 pulsa clock untuk mentransfer tiap bit, yang berarti dibutuhkan 8-pulsa clock untuk transfer 1 byte.

Data Serial dimasukkan ke shift register saat Clock naik. Lachched, Data Serial dipertahankan hingga Clock turun. Data Serial merupakan informasi yang ditampilkan.