Sistem Digital:Counter dan Adder: Difference between revisions

Created page with "==Rangkaian Counter== Pencacah (counter) adalah perangkat gerbang logika yang mengeluarkan data berurutan yang dipicu sinyal clock/pulsa. Counter adalah rangkaian logika sekuensial yang dapat berfungsi untuk menghitung jumlah sinyal clock/pulsa yang masuk dan dinyatakan dalam bentuk bilangan biner. Mencacah dapat diartikan menghitung, hampir semua sistem logika menerapkan pencacah. Fungsi dasar pencacah adalah untuk “mengingat” berapa banyak pulsa detak yang telah..." |

m Kangtain moved page Materi/Sistem Digital/Counter dan Adder to Sistem Digital:Counter dan Adder |

||

| (17 intermediate revisions by the same user not shown) | |||

| Line 7: | Line 7: | ||

Counter adalah rangkaian logika sekuensial yang dapat berfungsi untuk menghitung jumlah sinyal clock/pulsa yang masuk dan dinyatakan dalam bentuk bilangan biner. | Counter adalah rangkaian logika sekuensial yang dapat berfungsi untuk menghitung jumlah sinyal clock/pulsa yang masuk dan dinyatakan dalam bentuk bilangan biner. | ||

[[File:Rangkaian counter 1.png|thumb|center|400px]] | |||

IC 74LS90 berisikan rangkaian counter. | |||

<gallery> | |||

74LS90-Decade-Counte.png|IC 74LS90 Source: [https://sharvielectronics.com/wp-content/uploads/2020/02/74LS90-Decade-Counte.png sharvielectronics.com]. | |||

File:Rangkaian IC 74LS90.png|Rangkaian pada IC 74LS90. | |||

File:Rangkaian counter 2.png | |||

</gallery> | |||

==Rangkaian ADDER== | |||

Rangkaian Adder (penjumlah) adalah rangkaian elektronika digital yang digunakan untuk menjumlahkan dua buah angka (dalam sistem bilangan biner), sementara itu di dalam komputer rangkaian adder terdapat pada mikroprosesor dalam blok ALU (Arithmetic Logic Unit). | |||

Sistem bilangan yang digunakan dalam rangkaian adder adalah: | |||

*Sistem bilangan Biner (memiliki bilangan dasar 2) | |||

*Sistem bilangan Oktal (memiliki bilangan dasar 8) | |||

*Sistem bilangan Desimal (memiliki bilangan dasar 10) | |||

*Sistem bilangan Hexadesimal (memiliki bilangan dasar 16) | |||

===Half-adder=== | |||

[[File:Half adder.png|thumb|right|300px|Rangkaian Half-adder]] Berdasarkan dua input A dan B, outputnya adalah S (sum) yang dihitung berdasarkan implementasi operasi logika XOR dari A dan B. Selain Output S (sum), outputnya adalah C (carry) yang dihasilkan dari implementasi operasi logika AND. Disimpulkan S menyatakan hasil penjumlahan input A dan B, sedangakan C adalah menyatakan MSB (Most Significant Bit atau Carry bit) dari penjumlahan tersebut. | |||

{| class="wikitable" | |||

|+ | |||

|- | |||

! colspan="2" |Input !! colspan="2" |Output | |||

|- | |||

! A !! B !! C !! S | |||

|- | |||

| 0 || 0 || 0 || 0 | |||

|- | |||

| 1 || 0 || 0 || 1 | |||

|- | |||

| 0 || 1 || 0 || 1 | |||

|- | |||

| 1 || 1 || 1 || 0 | |||

|} | |||

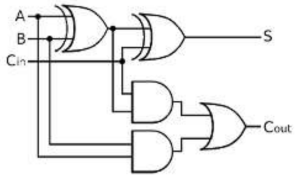

===Full-adder=== | |||

[[File:Full adderr.png|thumb|right|300px|Rangkaian Full Adder]]Berdasarkan dua input seperti half-adder, hanya saja Full-adder mampu menampung carry dari hasil penjumlahan sebelumnya. Sehingga dengan adanya carry tersebut, maka jumlah inputnya sewaktu-waktu bisa jadi 3 (tergantung kondisi carrynya). | |||

{| class="wikitable" | |||

|+ | |||

|- | |||

! colspan="3" |Input !! colspan="2" |Output | |||

|- | |||

! A || B || C<sub>in</sub> || C<sub>out</sub> || S | |||

|- | |||

| 0 || 0 || 0 || 0 || 0 | |||

|- | |||

| 1 || 0 || 0 || 0 || 1 | |||

|- | |||

| 0 || 1 || 0 || 0 || 1 | |||

|- | |||

| 1 || 1 || 0 || 1 || 0 | |||

|- | |||

| 0 || 0 || 1 || 0 || 1 | |||

|- | |||

| 1 || 0 || 1 || 1 || 0 | |||

|- | |||

| 0 || 1 || 1 || 1 || 0 | |||

|- | |||

| 1 || 1 || 1 || 1 || 1 | |||

|} | |||

[[Category:Materi]] | |||

Latest revision as of 22:20, 19 November 2022

Rangkaian Counter

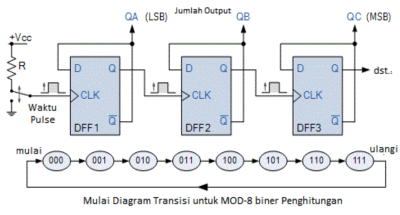

Pencacah (counter) adalah perangkat gerbang logika yang mengeluarkan data berurutan yang dipicu sinyal clock/pulsa.

Counter adalah rangkaian logika sekuensial yang dapat berfungsi untuk menghitung jumlah sinyal clock/pulsa yang masuk dan dinyatakan dalam bentuk bilangan biner.

Mencacah dapat diartikan menghitung, hampir semua sistem logika menerapkan pencacah. Fungsi dasar pencacah adalah untuk “mengingat” berapa banyak pulsa detak yang telah dimasukkan kepada masukan.

Counter adalah rangkaian logika sekuensial yang dapat berfungsi untuk menghitung jumlah sinyal clock/pulsa yang masuk dan dinyatakan dalam bentuk bilangan biner.

IC 74LS90 berisikan rangkaian counter.

-

IC 74LS90 Source: sharvielectronics.com.

-

Rangkaian pada IC 74LS90.

Rangkaian ADDER

Rangkaian Adder (penjumlah) adalah rangkaian elektronika digital yang digunakan untuk menjumlahkan dua buah angka (dalam sistem bilangan biner), sementara itu di dalam komputer rangkaian adder terdapat pada mikroprosesor dalam blok ALU (Arithmetic Logic Unit).

Sistem bilangan yang digunakan dalam rangkaian adder adalah:

- Sistem bilangan Biner (memiliki bilangan dasar 2)

- Sistem bilangan Oktal (memiliki bilangan dasar 8)

- Sistem bilangan Desimal (memiliki bilangan dasar 10)

- Sistem bilangan Hexadesimal (memiliki bilangan dasar 16)

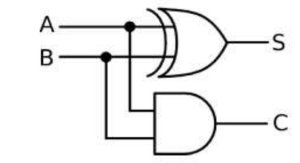

Half-adder

Berdasarkan dua input A dan B, outputnya adalah S (sum) yang dihitung berdasarkan implementasi operasi logika XOR dari A dan B. Selain Output S (sum), outputnya adalah C (carry) yang dihasilkan dari implementasi operasi logika AND. Disimpulkan S menyatakan hasil penjumlahan input A dan B, sedangakan C adalah menyatakan MSB (Most Significant Bit atau Carry bit) dari penjumlahan tersebut.

| Input | Output | ||

|---|---|---|---|

| A | B | C | S |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Full-adder

Berdasarkan dua input seperti half-adder, hanya saja Full-adder mampu menampung carry dari hasil penjumlahan sebelumnya. Sehingga dengan adanya carry tersebut, maka jumlah inputnya sewaktu-waktu bisa jadi 3 (tergantung kondisi carrynya).

| Input | Output | |||

|---|---|---|---|---|

| A | B | Cin | Cout | S |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |